# Impact of Contact on the Operation and Performance of Back-Gated Monolayer MoS<sub>2</sub> Field-Effect-Transistors

Wei Liu,\* Deblina Sarkar, Jiahao Kang, Wei Cao, and Kaustav Banerjee\*

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106, United States

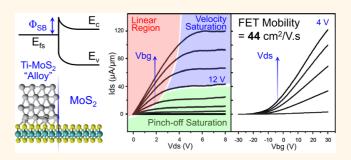

**ABSTRACT** Metal contacts to atomically thin two-dimensional (2D) crystal based FETs play a decisive role in determining their operation and performance. However, the effects of contacts on the switching behavior, field-effect mobility, and current saturation of monolayer MoS<sub>2</sub> FETs have not been well explored and, hence, is the focus of this work. The dependence of contact resistance on the drain current is revealed by four-terminal-measurements. Without high- $\kappa$  dielectric boosting, an electron mobility of 44 cm<sup>2</sup>/(V · s) has been achieved in a monolayer MoS<sub>2</sub> FET on SiO<sub>2</sub> substrate at room

temperature. Velocity saturation is identified as the main mechanism responsible for the current saturation in back-gated monolayer MoS<sub>2</sub> FETs at relatively higher carrier densities. Furthermore, for the first time, electron saturation velocity of monolayer MoS<sub>2</sub> is extracted at high-field condition.

**KEYWORDS:** 2D semiconductor · contact · current saturation · field-effect transistor · molybdenum disulfide · Schottky barrier · transition metal dichalcogenides

long with the continuous scaling of devices in the semiconductor industry, it is generally accepted that Si (including ultrathin Silicon-on-Insulator (SOI))-based complementary metal-oxidesemiconductor (CMOS) technology will reach its scaling limit (below 5 nm) due to the bulk nature of silicon.1 Therefore, new semiconductor materials alternate to silicon should be developed to avoid those scaling issues in Si-based CMOS technology. Monolayer MoS<sub>2</sub>, one of the transition-metal dichalcogenides (TMDs), shows great potential for nanoscale (sub-5 nm) FET applications owing to its atomic thickness (0.65 nm), excellent thermal stability, considerable band gap ( $\sim$ 1.8 eV), and pristine interfaces (without out-of-plane dangling bonds).<sup>1-4</sup> The atomically thin MoS<sub>2</sub> provides excellent gate electrostatic control to suppress shortchannel-effect (SCE),<sup>5,6</sup> which is one of the major issues in nanoscale MOSFETs. In addition, the large effective mass of monolayer MoS<sub>2</sub> can reduce the source/drain direct tunneling, thereby leading to small subthreshold swing (SS). Recently, monolayer MoS<sub>2</sub> FET has been experimentally demonstrated

with a small SS of 74 mV/decade, and an ON/OFF ratio of ~10<sup>8</sup>, indicating that monolayer MoS<sub>2</sub> is suitable for low-power digital applications.<sup>1–11</sup> However, the interface between 2D semiconductors and threedimensional (3D) metal contacts is one of the major parameters, which determines the performance of all 2D material based nanoelectronic devices.<sup>11–15</sup> This has been proved in several reported MoS<sub>2</sub> works,<sup>15,16</sup> in which contact resistances at the metal/ MoS<sub>2</sub> interfaces significantly limit the device performances.

Fermi level pinning is a common issue in low dimensional materials with metal contacts. It has been proved that there is severe Fermi level pinning between MoS<sub>2</sub> and metal.<sup>17</sup> Hence, Schottky barrier always exists between monolayer MoS<sub>2</sub> and contact metals. Although small Schottky barriers (30 meV with Sc and 50 meV with Ti) have been achieved between few-layer or multilayer MoS<sub>2</sub> and contact metals,<sup>18</sup> such small Schottky barriers still influence the device operation.<sup>19</sup> Compared with multilayer MoS<sub>2</sub>, monolayer MoS<sub>2</sub> has smaller electron affinity (4.2 eV). Therefore, according to

\* Address correspondence to liuwei@ece.ucsb.edu, kaustav@ece.ucsb.edu.

Received for review November 15, 2014 and accepted June 3, 2015.

Published online June 03, 2015 10.1021/nn506512j

© 2015 American Chemical Society

VOL.9 • NO.8 • 7904-7912 • 2015

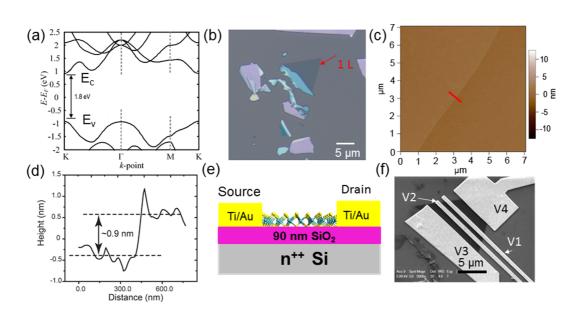

Figure 1. (a) Energy dispersion of monolayer  $MoS_2$ . Monolayer  $MoS_2$  has a direct band gap of 1.8 eV. (b) Optical microscope image of monolayer  $MoS_2$  on  $SiO_2$  (90 nm)/Si. (c) AFM image and (d) height profile of monolayer  $MoS_2$ . The height profile is measured along the red line in (c). (e) Schematic view of the back-gated monolayer  $MoS_2$  FET. (f) SEM image of the fabricated back-gated monolayer  $MoS_2$  FET. In four-terminal-measurements, current flows ( $I_{ds}$ ) from V4 to V3. The voltages are measured on V1 and V2. Channel resistance is calculated as  $(V1 - V2)/I_{ds}$ . The details of resistance extraction is shown in Supporting Information S2.

the Schottky theory, the Schottky barrier between monolayer  $MoS_2$  and Ti (work function = 4.33 eV) should be larger, thereby affecting the device performance to a greater extent. However, ambiguities still exist in the understanding of the nature and impact of such contacts on the characteristics and operation of monolayer  $MoS_2$  FETs, such as switching behavior, current saturation and field-effect mobility.

Various metals such as Ti, Au, Ni, Mo, and Sc have been used as the contact metal with monolayer or multilayer MoS<sub>2</sub>.<sup>2,5-19</sup> Recent theoretical and experimental works have shown that titanium (Ti) can form a good contact with monolayer MoS<sub>2</sub> (monolayer MoS<sub>2</sub> has a direct band gap of 1.8 eV (Figure 1a)),<sup>11,12</sup> in which Ti shows high capability to dope MoS<sub>2</sub> (under the contact region). Since Ti shows promise as a contact metal with MoS<sub>2</sub>, we select Ti as the contact metal to study the impact of contacts on the operation and performance of monolayer MoS<sub>2</sub> FETs. On the other hand, we observed a current degradation after depositing 30 nm HfO<sub>2</sub> dielectric film on top of monolayer MoS<sub>2</sub> (Supporting Information S1). Hence we choose backgated FET configuration to study the metal contact to MoS<sub>2</sub> and intrinsic mobility of MoS<sub>2</sub> in this work.

Monolayer films are prepared by mechanical exfoliation of bulk  $MoS_2$  (SPI Instrument, Inc.) onto 90 nm SiO<sub>2</sub>/Si (highly *n*-doped) substrate. The thickness of  $MoS_2$  film is identified using optical microscope (Figure 1b) since we have established the correlation between optical contrast of monolayer TMD and thickness of underlying dielectric.<sup>19</sup> The thickness of monolayer  $MoS_2$  is further confirmed by AFM (Figure 1c,d). The measured thickness of monolayer is around 0.9 nm due to the absorbed molecules on top of  $MoS_2$ . Heavily *n*-doped Si is used as the back gate as shown in Figure 1e. The SEM image of the fabricated back-gated FET device is shown in Figure 1f. After metal lift-off, device is loaded into Lakeshore vacuum probe station. All measurements are performed in vacuum  $(1 \times 10^{-6} \text{ mbar})$  at room temperature after annealing in the vacuum  $(3 \times 10^{-6} \text{ mbar})$  at 420 K for 12 h to remove any absorbed moisture and solvent molecules.

## **RESULTS AND DISCUSSION**

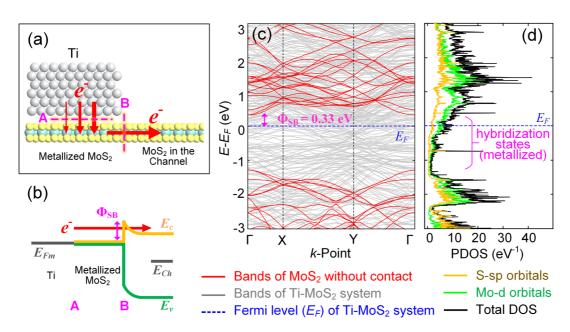

In a metal contact with  $MoS_2$  as shown in Figure 2a, there are two components contributing to the contact resistance, which are the tunneling barrier between metal and  $MoS_2$  below the contact metal due to the van der Waals (vdW) gap (dash line A in Figure 2a), and Schottky barrier between contact and channel (dash line B in Figure 2a). In this work, density functional theory (DFT) calculation is employed to explore the electronic nature of the contact between Ti and monolayer  $MoS_2$ . The details of the setup used for DFT calculations are included in the Supporting Information S3.

Electronic dispersion of  $MoS_2$  with Ti is studied to estimate the Schottky barrier between monolayer  $MoS_2$  and Ti by DFT as shown in Figure 2c. In Figure 2c, the red lines indicate the bands of monolayer  $MoS_2$  with a band gap of 1.8 eV. Gray lines show the bands of Ti- $MoS_2$  system, indicating that the original  $MoS_2$  bands (red) are completely disturbed by the Ti atoms due to strong hybridization between Ti and S orbitals. The new bands (gray) of the Ti- $MoS_2$  system display a metallic behavior with a zero band gap, implying that  $MoS_2$  under Ti area is completely metallized by the hybridization between Ti and S atoms. This metallization is also confirmed by the PDOS of the

VOL. 9 • NO. 8 • 7904-7912 • 2015

IAI

www.acsnano.org

Figure 2. (a) Schematic of electron injection direction in  $MoS_2$  and contact metal: A, tunneling barrier between metal and  $MoS_2$  below contact metal; B, Schottky barrier between contact and channel. (b) Band diagram illustrating the  $Ti-MoS_2$  Schottky barrier. (c) Electronic dispersion of  $MoS_2$  without contact (red lines) and with Ti contact (grey lines). (d) PDOS of sp orbital of S atoms (yellow line) and d orbital of Mo atoms (green line).

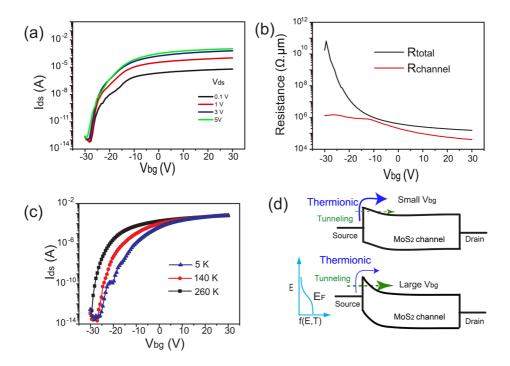

Figure 3. (a)  $I_{ds}-V_{bg}$  curve of monolayer MoS<sub>2</sub> back-gated FET with Ti contact. (b) Channel resistance ( $R_{channel}$ ), and total source-drain resistance ( $R_{total}$ ) as a function of back-gate voltage ( $V_{bg}$ ). (c) Temperature dependent  $I_{ds}-V_{bg}$  curves of back-gated monolayer MoS<sub>2</sub> FET with Ti contact,  $V_{ds}$  = 3 V. (d) Band diagram of MoS<sub>2</sub> back-gated FET with Ti contact at different  $V_{bg}$ .

Ti-MoS<sub>2</sub> system (Figure 2d). As shown in Figure 2d, the original band gap of MoS<sub>2</sub> vanishes after contacting with Ti. Hence, the tunneling barrier height is zero between Ti and MoS<sub>2</sub> due to the metallic behavior of Ti-MoS<sub>2</sub> system. Therefore, contact resistance is solely contributed by the Schottky barrier between the contact area (Ti-MoS<sub>2</sub> system) and the monolayer channel

$MoS_2$  (Figure 2b). By comparing the band structure of  $MoS_2$  (bottom of conduction band) with the Fermi level of Ti $-MoS_2$  system (given by DFT, Figure 2c), a 0.33 eV Schottky barrier can be extracted. This Schottky barrier (0.33 eV) is consistent with our experimental measurements that yielded 0.3–0.35 eV, which is shown in the next section.

VOL.9 • NO.8 • 7904-7912 • 2015 A

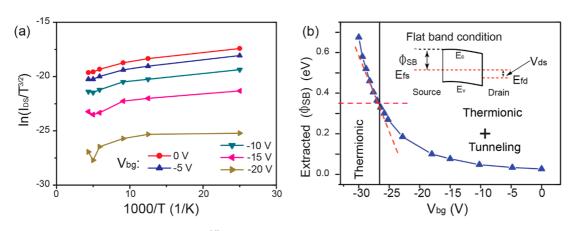

Figure 4. (a) Arrhenius-type plot of ln  $(I_{ds}/T^{3/2})$  vs 1000/T at different  $V_{bg}$ . (b) Extracted effective barrier height ( $\Phi_{SB}$ ) as a function of V<sub>bg</sub> for monolayer MoS<sub>2</sub> FET with Ti contact. Inset shows the band diagram at flat band condition.

Figure 3a shows the transfer characteristics of the back-gated monolayer MoS<sub>2</sub> FET with Ti (10 nm)/Au (100 nm) contact. It clearly displays an *n*-type behavior with ON/OFF ratios (defined as the ratio of maximum to minimum drive current in the  $V_{bq}$  range of -30 to 30 V) exceeding  $10^6$  at  $V_{ds}$  varying from 0.1 to 5 V. Fourterminal-measurements are employed to measure the  $R_{\text{channel}}$  as denoted by the red curve in Figure 3b. Black curve in Figure 3b corresponds to the  $R_{total}$  ( $R_{total}$  =  $2R_{\rm c} + R_{\rm channel} = V_{\rm ds}/I_{\rm ds}$ ) measured by two-terminal measurements (between V1 and V2 in Figure 1f) at  $V_{\rm ds} = 0.1$  V.  $R_{\rm total}$  shows a large variation, which is  $\sim 10^6$ for  $V_{bq}$  swept from -30 to 30 V. Hence, for back-gated monolayer MoS<sub>2</sub> FET with Ti contact, the switching mainly occurs due to modulating the contact.

To clearly understand the mechanism of current injection in monolayer MoS<sub>2</sub> FET with Ti contact, temperature dependent measurements are performed. Figure 3c shows the temperature dependent  $I_{ds} - V_{ba}$ curves of monolayer MoS<sub>2</sub> FET with Ti contact. When the  $V_{\rm bg}$  is below 10 V, the source drain current  $(I_{\rm ds})$ clearly shows temperature dependent behavior, indicating that thermionic emission dominates the electron injection at low  $V_{bq}$ . At high temperatures, electrons can occupy higher energy levels leading to more electrons flowing over the Schottky barrier and contributing to the current injection.  $I_{ds}$  becomes less dependent on the temperature when  $V_{ba}$  is above 10 V, implying that tunneling dominates the current at high  $V_{\rm bg}$  due to the narrowing of the Schottky barrier, which is created by the band bending near the MoS<sub>2</sub>-Ti contact (Figure 3d).<sup>17</sup>

Since the DFT calculation predicts a 0.33 eV Schottky barrier between Ti and monolayer MoS<sub>2</sub>, hence, in order to understand the Schottky barrier effect on monolayer MoS<sub>2</sub> FET operation, it is necessary to measure the Schottky barrier between Ti and monolayer MoS<sub>2</sub>. The expression of thermionic emission current for 2D material can be derived as  $I = A_{2D}WT^{3/2}e^{-(q\Phi_{SB}/K_BT)}(1 - e^{-(qV_{ds}/k_BT)})$ , where q is the magnitude of the electron charge,  $\Phi_{\text{SB}}$  is the Schottky

LIU ET AL.

barrier height, W is the width of the contact with 2D material,  $k_{\rm B}$  is the Boltzmann constant, and  $V_{\rm ds}$ is the drain-source bias. A<sub>2D</sub> is the Richardson's constant for 2D materials and is derived to be  $A_{2D}$  =  $\{[2(2\pi)^{1/2}g_{v}q\sqrt{m^{*}}]/h^{2}\}k_{B}^{3/2}$ , where  $g_{v}$  is the valley degeneracy, h is Planck's constant, and m\* is in-plane effective mass of monolayer MoS<sub>2</sub>. The derivation of thermionic emission current for 2D material is shown in the Supporting Information S4. By comparing the thermionic emission equations of 2D material and bulk material, one can find that temperature dependence is lower for 2D material compared to that of 3D material. In addition, the Richardson's constant is also different for 2D material and 3D material (with different units).<sup>20</sup>

Figure 4a shows the Arrhenius plot for various gate voltages, which is measured by two-probe measurement. The slope of the Arrhenius plot (Figure 4a) can be used to analyze the Schottky barrier from the thermionic emission theory. Schottky barrier height as a function of  $V_{bq}$  is shown in Figure 4b. As mentioned in ref 18, it is necessary to evaluate the flat-band gate voltage because it is a benchmark to identify the transition point between the tunneling current and the thermionic emission current. When the gate voltage is below the flat-band gate voltage, the thermionic emission predominantly contributes to the current. Hence, using the thermionic emission equation for 2D materials, the Schottky barrier between MoS<sub>2</sub> and Ti can be accurately extracted. The extracted Schottky barrier between monolayer MoS<sub>2</sub> and Ti varies from 0.3 to 0.35 eV measured from six different monolayer devices. The Schottky barrier between monolayer MoS<sub>2</sub> and Ti is significantly larger than the Schottky barrier between multilayer MoS<sub>2</sub> (bandgap: 1.2 eV) and Ti, which is around 50 meV.<sup>18</sup> The extracted Schottky barrier between monolayer MoS<sub>2</sub> and Ti is quite reasonable given that monolayer MoS<sub>2</sub> has smaller electron affinity than multilayer MoS<sub>2</sub>. The value of the Schottky barrier height is also consistent with the DFT calculation, which confirms the accuracy of our contact model.

VOL.9 • NO.8 • 7904-7912 • 2015 ACS

JAI

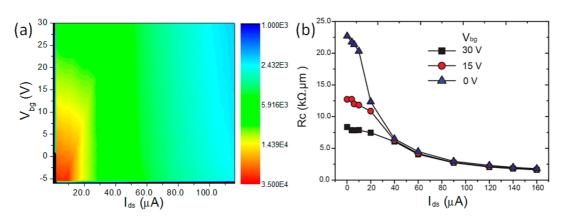

Figure 5. (a) Contour plot of  $R_c(\Omega \cdot \mu m)$  as a function of  $V_{bg}$  and  $I_{ds}$  used for the 4-point measurements. (b)  $R_c$  as a function of  $I_{ds}$  at various  $V_{bg}$ .

As mentioned above,  $MoS_2$  FET with Ti contact has a large Schottky barrier. To study the effect of contact on the performance of  $MoS_2$  FET, it is desirable to extract the contact resistance. Four-terminal-measurement method is employed to extract the contact resistance ( $R_c$ ) at various  $V_{bg}$ . By injecting a constant current ( $I_{ds}$ ) into the four-terminal configuration (between V4 and V3 in Figure 1f),  $R_{channel}$  (between the inner two electrodes, V1 and V2, as shown in Figure 1f) can be directly measured. Then,  $R_{total}$  ( $R_{total} = (V1 - V2)/I_{ds}$ ) between V1 and V2 is measured using two-terminal-measurements by applying the same current employed in the four-terminal-measurements. Hence,  $R_c$  can be extracted by subtracting the  $R_{channel}$  from  $R_{total}$ .

Figure 5a shows the contour plot of  $R_c$  as a function of  $V_{bg}$  and  $I_{ds}$  applied for the four-terminalmeasurements. It is found that  $R_c$  is dependent on the values of applied  $I_{ds}$  as well as the  $V_{bg}$  as shown in Figure 5a. At small  $I_{ds}$  (below 20  $\mu$ A),  $R_c$  shows strong  $V_{bg}$  dependence, in which  $R_c$  is ~25 k $\Omega \cdot \mu$ m at  $V_{bg} =$ -5 V, while  $R_c$  can be reduced to 7 k $\Omega \cdot \mu$ m at high  $V_{bg}$ (30 V). When  $I_{ds} > 40 \ \mu$ A,  $R_c$  is significantly reduced at low  $V_{bg}$  and shows less  $V_{bg}$  dependence.

Various  $R_c$ 's as a function of  $I_{ds}$  at  $V_{bg} = 0$ , 15, and 30 V are also plotted in Figure 5b. At low  $I_{ds}$  (<40  $\mu$ A),  $R_c$  shows distinct  $V_{bg}$  dependence, implying that Schottky barrier is mainly tuned by the gate electrostatics. However, when  $I_{ds} > 40 \ \mu$ A,  $R_c$  has less dependence on the  $V_{bg}$ , indicating that the amount of electrons injected from source is much larger than the electrons generated by gate electrostatics. Hence, the large amount of electrons injected from source can heavily dope monolayer MoS<sub>2</sub> resulting in a very narrow Schottky barrier. The minimum extracted  $R_c$ is ~1.3 k $\Omega \cdot \mu m$  ( $I_{ds} = 150 \ \mu$ A,  $V_{bg} = 30$  V), which is much smaller than any reported value on metal contact with monolayer MoS<sub>2</sub>.

Current saturation of MoS<sub>2</sub> FET is important for digital circuit applications (shown in Supporting Information S5), in which it can significantly influence the noise margins.<sup>4</sup> The saturation performance, which can

be described by output resistance, determines sharpness of the voltage-transfer curve of a CMOS inverter, and thus the maximum noise margin. Although the atomic scale thickness of monolayer MoS<sub>2</sub> provides excellent electrostatics, current saturation in monolayer MoS<sub>2</sub> back-gated FETs has been rarely observed at low  $V_{ds}$ .<sup>21</sup> As mentioned in our previous work, due to the high parasitic series source/drain contact resistance,<sup>15,19</sup> the effective  $V_{gs}$  and  $V_{ds}$  are lowered and are given by  $V_{gs\_eff} = V_{gs} - (R_c \times I_{ds})$  and  $V_{ds\_eff} = V_{ds} - (2R_c \times I_{ds})$ .  $R_c$  can be directly extracted from Figure 5a at given  $V_{bg}$  and  $I_{ds}$ . This provides the possibility to study the performance of the MoS<sub>2</sub> FET.

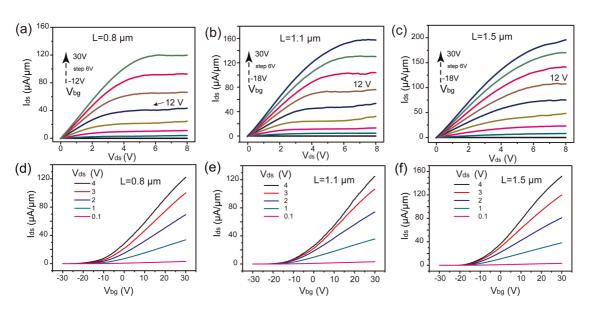

Figure 6a-c shows the output characteristics of monolayer MoS<sub>2</sub> FETs with a channel length of 0.8, 1.1, and 1.5  $\mu$ m, respectively. All of the three  $I_{ds}-V_{ds}$ curves display a nearly linear behavior at low  $V_{ds}$ , indicating that the Schottky barrier is very narrow. The lowest  $R_c$  of our device is ~1.3 k $\Omega \cdot \mu m$  with Ti contact at  $V_{bg} = 30$  V. Due to this small  $R_{cr}$  ON-current of our monolayer MoS<sub>2</sub> FET is  $\sim$ 50  $\mu$ m/ $\mu$ A at V<sub>bg</sub> = 30 V and  $V_{ds} = 2V$  (or 200  $\mu$ A/ $\mu$ m at V<sub>bg</sub> = 30 V and V<sub>ds</sub> = 8 V) which is much higher than any reported values in backgated monolayer  $MoS_2$  FETs. With a small  $R_c$ , robust current saturation can be observed in Figure 6a. However, along with the increase of the channel length, current saturation degrades at high  $V_{\rm bg}$  for long channel devices (Figure 6b,c), implying the absence of "pinch-off".

In Figure 6a–c, monolayer MoS<sub>2</sub> FETs have a pinchoff like current saturation when  $V_{bg} < 12$  V, in which  $I_{ds}$ increases along with increase of  $V_{ds}$  until the saturation value is reached. The drain voltages also satisfy pinch-off saturation condition,  $V_{ds\_eff} > (V_{gs\_eff} - (R_c \times I_{ds} - V_{th}))/m$ . Here, *m* is the body-effect coefficient that can be derived from subthreshold swing (SS) equation: SS =  $2.3(1 + C_{trap}/C_{ox})mkT/q = 2.3mkT/q$ , where  $C_{trap}$  is interface trap capacitance,  $C_{ox}$  is gate dielectric capacitance, *k* is Boltzmann's constant, *T* is temperature and *q* is electronic charge. The SS of our back-gated FET is around 410 mV/dec. Hence, *m* is around 7, which

Figure 6. (a-c) Output characteristics of back-gated monolayer MoS<sub>2</sub> FETs. (d-f) Transfer characteristics of back-gated monolayer MoS<sub>2</sub> FETs measured from device (a), (b), and (c), respectively.

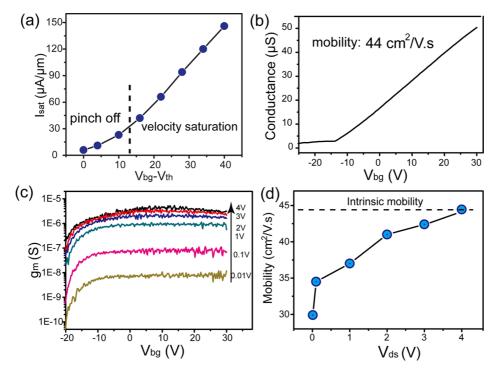

Figure 7. (a) Corresponding  $I_{sat}$  as a function of  $(V_{bg}-V_{th})$  extracted from device in Figure 6a. (b) Channel conductance (G) of monolayer MoS<sub>2</sub> FET with Ti contact as a function of  $V_{bg}$ . Values of G are measured by four-terminal-measurements.  $G=1/R_{channel}$ . (c) Transconductance ( $g_m$ ) of monolayer MoS<sub>2</sub> FET as a function of  $V_{bg}$  for various  $V_{ds}$ . (d) FET mobility (without excluding the effect of contacts) of monolayer MoS<sub>2</sub> as a function of  $V_{ds}$ .

indicates a poor gate modulation effect in back-gated FET. The threshold voltage ( $V_{\rm th}$ ) of our back gated device is approximately -10 V as shown in Figure 6d–f.  $R_{\rm c}$  can roughly be extracted from Figure 5a. In Figure 6a, when  $V_{\rm bg} = 18$  V and  $I_{\rm sat} = 60 \,\mu A/\mu m$  ( $V_{\rm ds} = 4$  V, width of the device is  $1.5 \,\mu m$ ),  $R_{\rm c}$  is  $\sim 2.5 \,\rm k\Omega \cdot \mu m$ . Hence, the ratio between  $R_{\rm c}$  and  $R_{\rm total}$  is  $\sim 3 \times 10^{-2}$  which indicates that  $R_{\rm c}$  has minimal impact on the ON-current of this device when the channel is fully turned on by the gate.

When  $V_{bg} < 12$  V,  $I_{ds}$  increases parabolically along with the increase of  $V_{ds}$  until the saturation value is reached. When  $V_{bg} > 12$  V,  $I_{ds}$  increases linearly and is proportional to the  $(V_{bg}-V_{th})$  as shown in Figure 7a, indicating that device is operated in the velocity saturation region. Four-terminal-measurements also confirm the linear behavior of the conductance as a function of  $V_{bg}$  when  $V_{bg} > 12V$  (Figure 7b). Hence, the current saturation in monolayer MoS<sub>2</sub> is a

VOL.9 • NO.8 • 7904-7912 • 2015

combination of pinch off (at low carrier density) and velocity saturation (at relatively higher carrier density).

For  $V_{bg} > 12$  V and  $V_{ds} > 4$  V,  $I_{ds}$  starts to saturate due to velocity saturation. Using equation for current ( $I_{sat}$ ) under velocity saturation  $I_{sat} = WC_{ox}(V_{effec\_bg} - V_{th} - V_{effec\_sat}/2)v_{sat}$ , where W is the width of device, and  $v_{sat}$ is the saturation velocity, the  $v_{sat}$  for monolayer MoS<sub>2</sub> is extracted from Figure 6a to be ~9.85 × 10<sup>5</sup> cm/s at  $V_{bg} = 30$  V and  $V_{ds} = 6$  V, which is close to the theoretically calculated value of ~10<sup>6</sup> cm/s.<sup>22,23</sup>

To improve the drive current for high-performance CMOS applications at ultrascaled dimensions, it is necessary to have high mobility.<sup>24</sup> However, one issue of monolayer MoS<sub>2</sub> is the low mobility, which is in the range of 0.1–13 cm<sup>2</sup>/(V·s) on SiO<sub>2</sub> substrate at room temperature.<sup>1,2</sup> In general, the Schottky barrier at the monolayer MoS<sub>2</sub>-Ti interface (area B as shown in Figure 2b) introduces a contact resistance that degrades the device performance. Although doping the source/drain area can significantly reduce the contact resistance, currently a reliable technique such as ion implantation to dope the 2D semiconductors without disrupting their desired properties (replacing any atoms destroys the electronic structure of 2D semiconductors) is lacking. Thus, it is necessary to estimate the effect of contact on the extracted FET mobility for the measurements and maximize the performance of monolayer MoS<sub>2</sub> FETs using the gate electrostatic doping that can thin down the tunneling barrier for electron injection. To estimate the effect of contact on the device performance, we first discuss the intrinsic mobility of monolayer MoS<sub>2</sub> flakes on SiO<sub>2</sub> (90 nm)/Si substrate measured in a four-terminal configuration followed by the analysis of effective mobility (including the effect of contact resistance) measured in a twoprobe configuration.

The channel conductance (G) of monolayer  $MoS_2$ FET as a function of  $V_{bq}$  is measured by four-terminalmeasurements. Then, the intrinsic mobility of monolayer MoS<sub>2</sub> can be extracted as  $\mu = (L/W) dG/dV_{bg}C_{ox}^{-1}$ in the linear region (Figure 7b), where  $C_{ox}$  (3.84  $\times$  $10^{-4}$  F·m<sup>-2</sup>) (the fringing capacitance and guantum capacitance can be ignored for a long channel backgated FET with thick dielectric film) is the capacitance of the 90 nm-thick bottom SiO<sub>2</sub> dielectric; L and W represent the length and width of the channel, respectively. The mobility of monolayer MoS<sub>2</sub> FET is ~44 cm<sup>2</sup>/(V·s) (deducting the effect of contact resistance) at room temperature, which is significantly higher than other reported values  $(0.1-13 \text{ cm}^2/(\text{V}\cdot\text{s}))$ in literature.<sup>1,2,25,26</sup> This value is also close to the mobility of monolayer MoS<sub>2</sub> after boosting with high-k dielectrics,<sup>5</sup> indicating that there is additional space to further improve the performance of monolayer MoS<sub>2</sub> on SiO<sub>2</sub> substrates. Additionally, as shown in Figure 7b, the conductance is linear over a relatively

large range of the back-gate voltage (from -10 to +30 V), indicating that the inherent 2D carrier density remains low. To verify this, the carrier density of monolayer back gated MoS<sub>2</sub> FET is calculated using the method described in ref 4. As shown in the Supporting Information S6, the carrier density of back-gated monolayer MoS<sub>2</sub> FET is linearly dependent on the gate voltage when the gate voltage is greater than the threshold voltage. The calculated carrier density is on the order of ~10<sup>13</sup>/cm<sup>2</sup> (which is considered low) because of the thick dielectric substrate (90 nm SiO<sub>2</sub>).

Since the intrinsic mobility of MoS<sub>2</sub> on SiO<sub>2</sub> has been calculated, we can estimate the effect of contact resistance on the mobility extracted through twoterminal measurements. Transconductance  $(q_m)$  for various drain voltages are measured through twoterminal measurements as shown in Figure 7c. At high  $V_{\rm ds}$ , the changes of  $g_{\rm m}$  tend to saturate. The maximal derived  $g_{\rm m}$  at  $V_{\rm ds}$  = 4 V is ~4.8  $\mu$ S/ $\mu$ m. Then, for twoterminal measurements, mobility can be extracted using the well-known equation:  $\mu = (L/W)g_mC_{ox}^{-1}V_{ds}^{-1}$  in the linear region of the  $I_{ds} - V_{ds}$  plot without deducting the contact resistance. Figure 7d shows the peak mobility for different V<sub>ds</sub>. The extracted effective mobility shows a clear  $V_{ds}$  dependency (Figure 7d). The extracted effective mobility is around 30 cm<sup>2</sup>/(V · s) at  $V_{ds} = 0.01$  V, while the mobility reaches 44 cm<sup>2</sup>/(V·s) at  $V_{ds}$ = 4 V, which is nearly equal to the intrinsic mobility of monolayer MoS<sub>2</sub> as shown in Figure 7c. This can be attributed to the reduction of Schottky-Barrier width on channel-source side with increase in  $V_{ds}$ , indicating that the channel is not efficiently controlled by the back gate with thick gate dielectric. In addition, under high electric field, electrons have high velocity resulting in the reduction of electron localization in MoS<sub>2</sub> system, since electron localization caused by the trapped charges in the SiO<sub>2</sub> substrate are responsible for the low mobility in monolayer MoS<sub>2</sub> FET.<sup>27</sup>

### CONCLUSION

In summary, the contact between Ti and MoS<sub>2</sub> dominates the switching of monolayer MoS<sub>2</sub> FETs. Schottky barrier between MoS<sub>2</sub> and Ti is accurately evaluated by 2D material thermionic emission current equation at flat-band gate voltage. The extracted contact resistance shows an obvious dependence on the drain current in four-terminal-measurements. In spite of a high Schottky barrier (0.3-0.35 eV), a small contact resistance  $\sim$ 1.3 k $\Omega$ · $\mu$ m can be achieved between monolayer MoS<sub>2</sub> and Ti, which is mainly due to the thinning of the Schottky barrier by the gate voltage. A record intrinsic mobility  $\sim$ 44 cm<sup>2</sup>/(V  $\cdot$  s) and record high ON-current (200  $\mu$ A/ $\mu$ m at V<sub>bg</sub> = 30 V and V<sub>ds</sub> = 8 V) in a monolayer back-gated MoS<sub>2</sub> FET on SiO<sub>2</sub> substrate have been observed at room temperature. In addition, the effective mobility of monolayer MoS<sub>2</sub> FET shows a clear drain voltage dependency, which is mainly from the

poor gate modulation as well as electron localization in  $MoS_2$ . In a back-gated monolayer  $MoS_2$  FET with 90 nm  $SiO_2$  back gate dielectric layer, velocity saturation is the main reason responsible for current saturation at relatively higher carrier density. Electron saturation velocity

of monolayer MoS<sub>2</sub> is extracted to be  $\sim 9.85 \times 10^5$  cm/s at  $V_{\rm bg} = 30$  V and  $V_{\rm ds} = 6$  V based on the electrical measurements. This work will provide useful guidance for the design of high performance monolayer MoS<sub>2</sub> FET for digital applications.

## EXPERIMENTAL SECTION

**Device Fabrication and Characterization.** The source and drain regions are defined by electron-beam lithography followed by Ti metallization. Subsequently, 100 nm Au film is deposited on 10 nm Ti film by electron beam evaporation at  $6 \times 10^{-7}$  mbar. Heavily *n*-doped Si is used as the back gate. After metal lift-off, device is loaded into Lakeshore vacuum probe station. All measurements are performed in vacuum ( $1 \times 10^{-6}$  mbar) at room temperature after annealing at 420 K for 12 h to remove any absorbed moisture and solvent molecules.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. This work was supported by the Air Force Office of Scientific Research, Arlington, VA, USA, under Grant FA9550-14-1-0268 (R18641). All process steps for device fabrication were carried out using the Nanostructure Cleanroom Facility at the California NanoSystems Institute and the Nanofabrication Facilities at UCSB, part of the National Nanotechnology Infrastructure Network. The authors made extensive use of the MRL Central Facilities at UCSB, which are supported by the MRSEC Program of the NSF (under Award No. DMR 1121053), a member of the NSF-funded Materials Research Facilities Network (www.mrfn.org).

Supporting Information Available: Gate modulation of top-gated monolayer FET with a thin high-K dielectric film, resistance extraction method, details of DFT calculations, derivation of thermionic-emission-current equation for 2D material, impact of current saturation on the performance of digital circuits, and carrier density of back-gated monolayer MoS<sub>2</sub> FET. The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/nn506512j.

#### **REFERENCES AND NOTES**

- leong, M.; Doris, B.; Kedzierski, J.; Rim, K.; Yang, M. Silicon Device Scaling to the Sub-10-nm Regime. *Science* 2004, 306, 2057–2060.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6, 147–150.

- Cao, W.; Kang, J.; Sarkar, D.; Liu, W.; Banerjee, K. Performance Evaluation and Design Considerations of 2D Semiconductor Based FETs for Sub-10 nm VLSI. *IEEE Int. Electron Devices Meet.* 2014, 729–732.

- Cao, W.; Kang, J.; Liu, W.; Banerjee, K. A Compact Current– Voltage Model for 2D Semiconductor Based Field-Effect Transistors Considering Interface Traps, Mobility Degradation, and Inefficient Doping Effect. *IEEE Trans. Electron Devices* 2014, 61, 4282–4290.

- Radisavljevic, B.; Kis, A. Mobility Engineering and a Metal– Insulator Transition in Monolayer MoS<sub>2</sub>. *Nat. Mater.* 2013, 12, 815–820.

- Sarkar, D.; Liu, W.; Xie, X.; Anselmo, A.; Mitragotri, S.; Banerjee, K. MoS<sub>2</sub> Field-Effect Transistor for Next-Generation Label-Free Biosensors. ACS Nano 2014, 8, 3992–4003.

- Radisavljevic, B.; Whitwick, M. B.; Kis, A. Integrated Circuits and Logic Operations Based on Single-Layer MoS<sub>2</sub>. ACS Nano 2011, 5, 9934–9938.

- 8. Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer  $MoS_2$  Transistors Be? Nano Lett. **2011**, *11*, 3768–3773.

- Xie, X.; Sarkar, D.; Liu, W.; Kang, J.; Marinov, O.; Deen, M. J.; Banerjee, K. Low-Frequency Noise in Bilayer MoS<sub>2</sub> Transistor. ACS Nano 2014, 8, 5633–5640.

- Sarkar, D.; Xie, X.; Kang, J.; Zhang, H.; Liu, W.; Navarrete, J.; Moskovits, M.; Banerjee, K. Functionalization of Transition Metal Dichalcogenides with Metallic Nanoparticles: Implications for Doping and Gas-Sensing. *Nano Lett.* 2015, *15*, 2852–2862.

- Kang, J.; Sarkar, D.; Liu, W.; Jena, D.; Banerjee, K. A Computational Study of Metal-Contacts to Beyond-Graphene 2D Semiconductor Materials. *IEEE Int. Electron Devices Meet.* 2012, 17.4.1–17.4.4.

- Popov, I.; Seifert, G.; Tománek, D. Designing Electrical Contacts to MoS<sub>2</sub> Monolayers: A Computational Study. *Phys. Rev. Lett.* 2012, 108, 156802.

- Fang, H.; Tosun, M.; Seol, G.; Chang, T. C.; Takei, K.; Guo, J.; Javey, A. Degenerate n-Doping of Few-Layer Transition Metal Dichalcogenides by Potassium. *Nano Lett.* **2013**, *13*, 1991–1995.

- Fang, H.; Chuang, S.; Chang, T. C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> P-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792.

- Liu, W.; Kang, J.; Sarkar, D.; Khatami, Y.; Jena, D.; Banerjee, K. Role of Metal Contacts in Designing High-Performance Monolayer n-Type WSe<sub>2</sub> Field Effect Transistors. *Nano Lett.* 2013, *13*, 1983–1990.

- Kang, J.; Liu, W.; Banerjee, K. High-Performance MoS<sub>2</sub> Transistors with Low-Resistance Molybdenum Contacts. *Appl. Phys. Lett.* **2014**, *104*, 093106.

- Kang, J.; Liu, W.; Sarkar, D.; Jena, D.; Banerjee, K. Computational Study of Metal Contacts to Monolayer Transition-Metal Dichalcogenide Semiconductors. *Phys. Rev. X* 2014, 4, 031005.

- Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2012**, *13*, 100–105.

- Liu, W.; Kang, J.; Cao, W.; Sarkar, D.; Khatami, Y.; Jena, D.; Banerjee, K. High-Performance Few-Layer-MoS<sub>2</sub> Field-Effect-Transistor with Record Low Contact-Resistance. *IEEE Int. Electron Devices Meet.* **2013**, 499–502.

- Roccaforte, F.; La Via, F.; Raineri, V.; Pierobon, R.; Zanoni, E. Richardson's Constant in Inhomogeneous Silicon Carbide Schottky Contacts. J. Appl. Phys. 2003, 93, 9137– 9144.

- Lee, H. S.; Min, S.-W.; Chang, Y.-G.; Park, M. K.; Nam, T.; Kim, H.; Kim, J. H.; Ryu, S.; Im, S. MoS<sub>2</sub> Nanosheet Phototransistors with Thickness-Modulated Optical Energy Gap. *Nano Lett.* **2012**, *12*, 3695–3700.

- Li, X.; Mullen, J. T.; Jin, Z.; Borysenko, K. M.; Nardelli, M. B.; Kim, K. W. Intrinsic Electrical Transport Properties of Monolayer Silicene and MoS<sub>2</sub> from First Principles. *Phys. Rev. B* 2013, *87*, 115418.

- Liu, L.; Bala Kumar, S.; Ouyang, Y.; Guo, J. Performance Limits of Monolayer Transition Metal Dichalcogenide Transistors. *IEEE Trans. Electron Devices* 2011, *58*, 3042– 3047.

- Yeo, Y.; Lu, Q.; King, T.; Hu, C.; Kawashima, T.; Oishi, M.; Mashiro, S.; Sakai, J. Enhanced performance in sub-100 nm CMOSFETs using strained epitaxial silicon-germanium. *IEEE Int. Electron Devices Meet.* 2000, 753–756.

- Late, D. J.; Liu, B.; Matte, H. R.; Dravid, V. P.; Rao, C. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 2012, 6, 5635–5641.

7911

- 26. Amani, M.; Chin, M. L.; Birdwell, A. G.; O'Regan, T. P.; Najmaei, S.; Liu, Z.; Ajayan, P. M.; Lou, J.; Dubey, M. Electrical Performance of Monolayer MoS<sub>2</sub> Field-Effect Transistors Prepared by Chemical Vapor Deposition. *Appl. Phys. Lett.* **2013**, *102*, 193107.

- Ghatak, S.; Pal, A. N.; Ghosh, A. Nature of Electronic States in Atomically Thin MoS<sub>2</sub> Field-Effect Transistors. ACS Nano **2011**, *5*, 7707–7712.

JAN